この記事は、oneapi-src/oneAPI-samples (英語) で公開されている Adaptive Noise Reduction Sample を iSUS で翻訳した日本語参考訳です。原文は更新される可能性があります。原文と翻訳文の内容が異なる場合は原文を優先してください。

この Adaptive Noise Reduction (ANR) サンプルは、フィールド・プログラマブル・ゲート・アレイ (FPGA) 向けに高度に最適化されたイメージセンサー適応型ノイズ低減アルゴリズムを示すリファレンス・デザインです。

| 内容 | 説明 |

|---|---|

| ガイドの内容 | FPGA 上で適応型ノイズ低減 (ANR) アルゴリズムを実装する、パラメーター化可能なイメージ処理パイプラインを作成します。 |

| 所要時間 | ~ 1 時間 |

目的

この FPGA リファレンス・デザインは、バイラテラル・フィルターを使用して適応型ノイズ低減 (ANR) アルゴリズムを実装する、パラメーター化可能なイメージ処理パイプラインを示します。

ANR アルゴリズム自体と FPGA への実装の詳細については、以下の主要な実装の詳細を参照してください。

要件

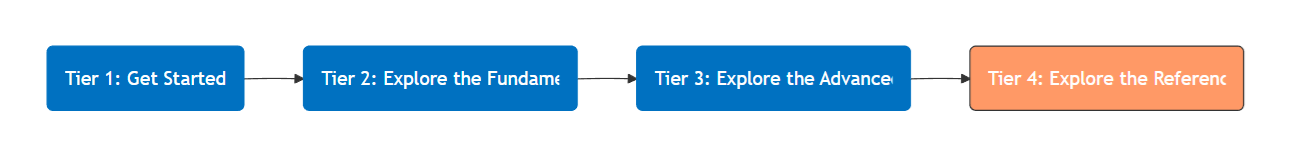

このサンプルは、FPGA サンプルコードの一部です。これは、リファレンス・デザインを示す Tier 4 サンプルに分類されます。

サンプルコードのこの部分をナビゲートする方法の詳細については、FPGA のトップレベルにある README.md (英語) を参照してください。また、ビルドエラーのトラブルシューティング (英語) 、インテル® DevCloud でのサンプルの実行 (英語) 、サンプルコードを使用した Visual Studio Code の使用 (英語)、選択したドキュメントへのリンク (英語) などに関する詳細情報も見つかります。

| 最適化 | 説明 |

|---|---|

| OS | Ubuntu 20.04 RHEL/CentOS 8 SUSE 15 Windows 10 Windows Server 2019 |

| ハードウェア | インテル® Agilex® 7、Arria® 10、および Stratix® 10 FPGA |

| ソフトウェア | インテル® oneAPI DPC++/C++ コンパイラー |

注: インテル® oneAPI DPC++/C++ コンパイラーは、エミュレーション用のコンパイル、レポートの生成、RTL の生成には十分ですが、シミュレーション・フローと FPGA コンパイルには追加のソフトウェアが必要です。

シミュレーター・フローを使用するには、インテル® Quartus® Prime Pro エディションと次のいずれかのシミュレーターがインストールされ、PATH によりアクセスできる必要があります:

- Questa – インテル® FPGA エディション

- Questa – インテル® FPGA スターター・エディション

- ModelSim® SE

ハードウェア・コンパイル・フローを使用には、インテル® Quartus® Prime Pro エディションがインストールされ、PATH 経由でアクセスできる必要があります。

警告: ターゲットとする FPGA に関連付けられたデバイスファイルを、インテル® Quartus® Prime インストールに必ず追加してください。

主な実装の詳細

ANR アルゴリズム

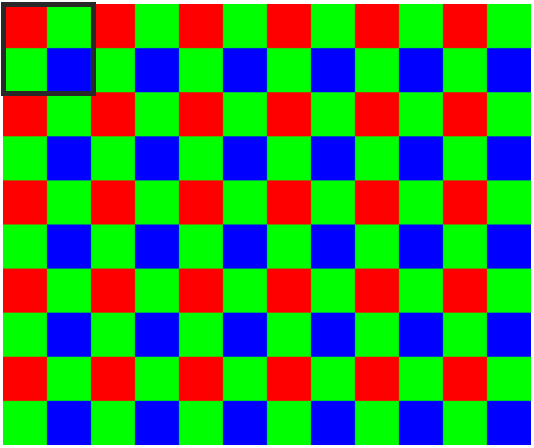

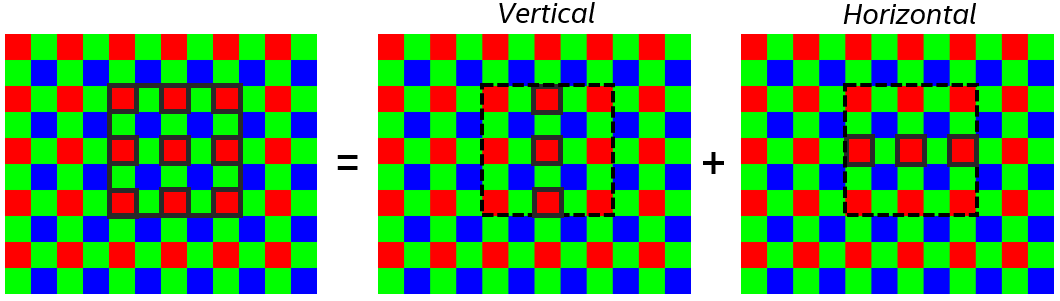

適応型ノイズ低減 (ANR) アルゴリズムは、ベイヤー形式の入力イメージを使用します (詳細については、Wikipedia のベイヤーフィルターの記事を参照してください)。各ピクセルに赤、緑、青の値 (RGB) が含まれる、PNG や JPG などのイメージ形式とは異なり、ベイヤー形式のイメージの各ピクセルは赤、緑、青のいずれかになります (次のイメージを参照してください)。RGB イメージに変換するには、4×4 の正方形を操作し、2 つの緑のピクセルを平均化して RGB ピクセルを生成します。この形式の目的は、人間の目は緑に対してより敏感であるため、より多くのピクセルを緑に割り当てることです。

ANR アルゴリズムはバイラテラル・フィルターを使用します。一方的フィルター (ボックスぼかしやガウスぼかしなど) は、特定のピクセルの強度を、隣接するピクセルの加重平均に置き換えます。隣接するそれぞれのピクセルの重みは、計算対象のピクセルからの空間距離によって異なります。この設計で使用されるバイラテラル・フィルターでは、各隣接ピクセルの重みは空間距離とピクセル強度の差の両方によって決まります。この違いにより、バイラテラル・フィルターはシャープなエッジを適切に保持できるようになります。(詳細については、Wikipedia のバイラテラル・フィルター (英語) 、ボックスブラー (英語) 、ガウシアンぼかしの記事を参照してください。)

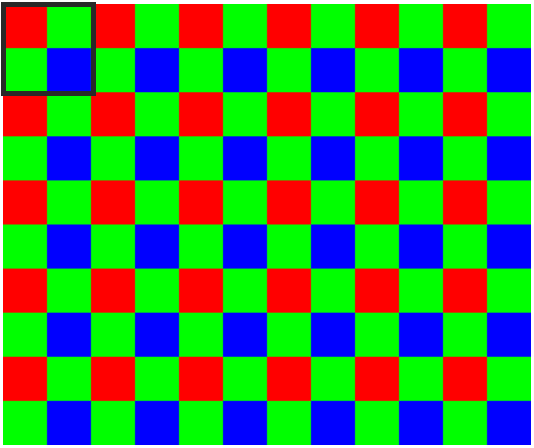

バイラテラル・フィルターは非線形であるため、分離できません。5×5 ウィンドウ (以下に表示) の場合、計算には 9 ピクセル (25 ピクセルではなく) のみが使用されます。この違いはベイヤーイメージ形式によるものです。最も正確なアプローチは、バイラテラル・フィルター・ウィンドウを生成し、指定されたピクセルカラー (下の画像では赤) のウィンドウ全体を一度に結合して出力ピクセル (中央のピクセル) を生成することです。5×5 の場合、合計する乗算は 9 回になります。

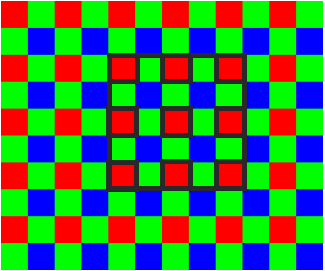

これにより、乗算結果を合計する加算器の長いチェーンが生成されます。この設計では、バイラテラル・フィルターを分離することで近似します。最初のステップでは、下のイメージに示すように、中央のピクセルに 1D 垂直フィルターを適用し、次に 1D 水平フィルターを適用します。このアプローチにより、合計する乗算の回数が 3 に減ります。デザインのコードは、すべてのピクセルに垂直フィルターを適用し、次に水平フィルターを適用します。その結果、コーナーのピクセルが間接的に中央のピクセルに重みを適用します。

ANR FPGA デザイン

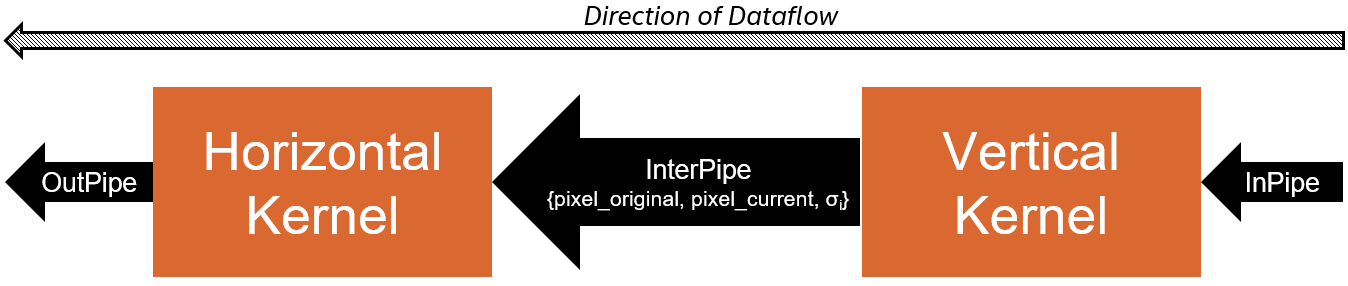

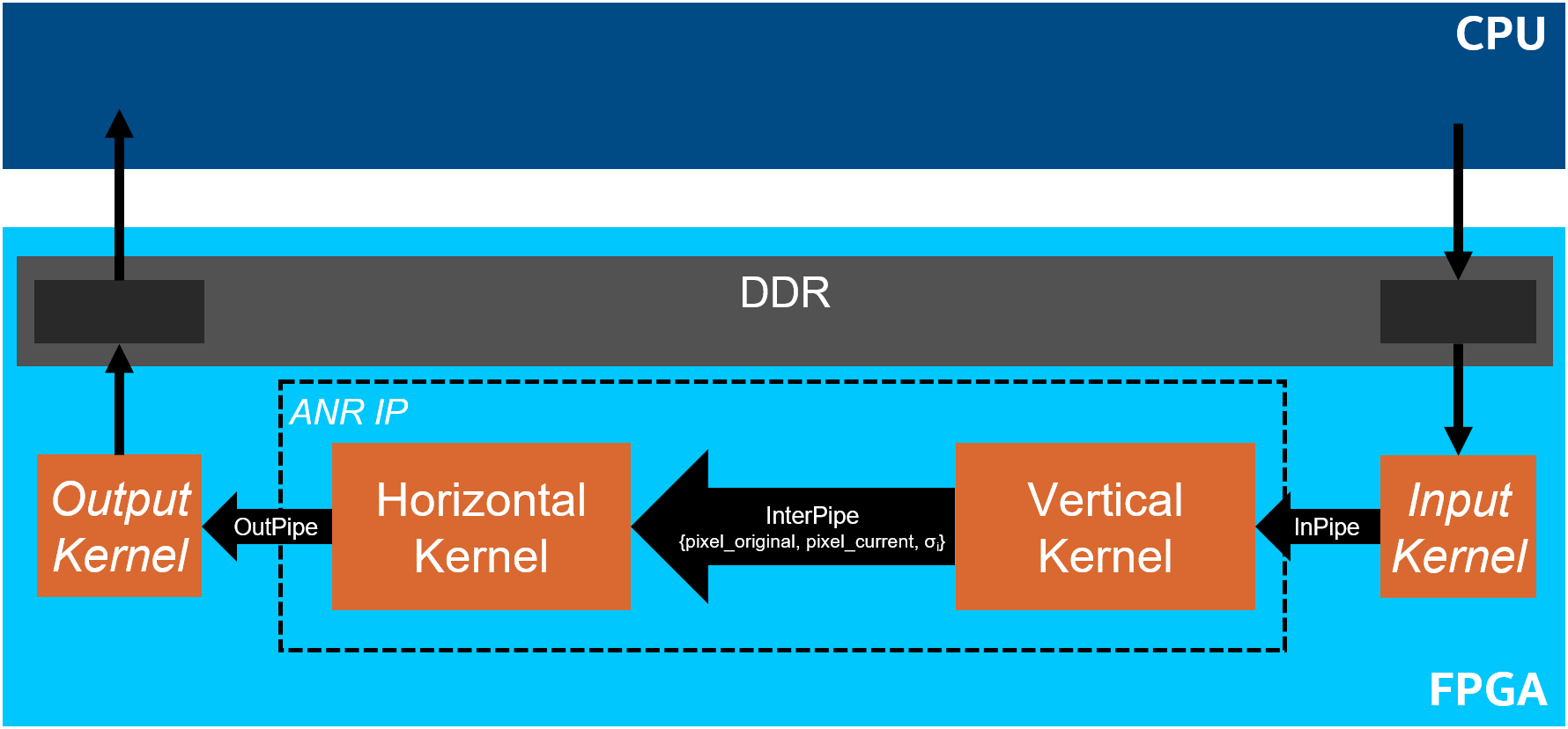

ANR アルゴリズムは、下の図に示すように、入力ピクセルが入力パイプを介してストリーミングされ、ノイズ除去された出力ピクセルが出力パイプからストリーミングされるカーネルシステムとして設計されています。設計は、次の図に示すように、内部 SYCL パイプによって接続された 2 つのカーネル Vertical Kernel と Horizontal Kernel で構成されています。Vertical Kernel は、現在のピクセルに基づいて強度シグマ値を計算し、バイラテラル・フィルターを計算し、それを現在のウィンドウに適用して中間ピクセル値を生成します。Vertical Kernel カーネルは、元のピクセル値、現在のピクセル値 (計算された中間ピクセル)、および強度シグマ値の 3 つの値を内部パイプを通じて送信します。これらのタプル内の Horizontal Kernel ストリームは、水平ウィンドウで同様の計算を行います。アルゴリズムは、転送された強度シグマ値を使用してバイラテラル・フィルターを計算し、新しいピクセル値でバイラテラル・フィルターの計算を行い、元のピクセルを使用してアルファー・ブレンディングを実行します。出力ピクセルは、元のピクセル値とノイズ除去されたピクセル値の加重パーセンテージになります。

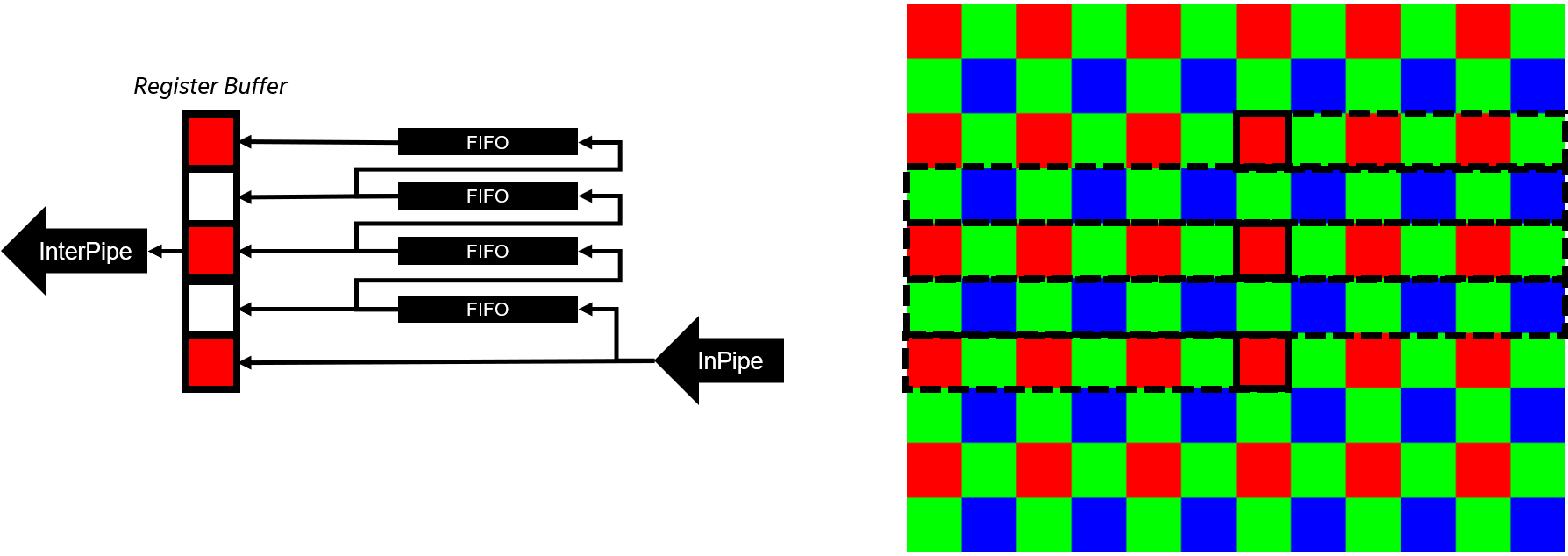

特定のピクセルを計算するには、Vertical Kernel は入力イメージの前の行 (ライン) を保存する必要があります。(イメージはそのテクニックを示します。)ピクセルはパイプからストリーミングされ、前の行のピクセルとともに使用され、1D 垂直ウィンドウ操作が実行されます。

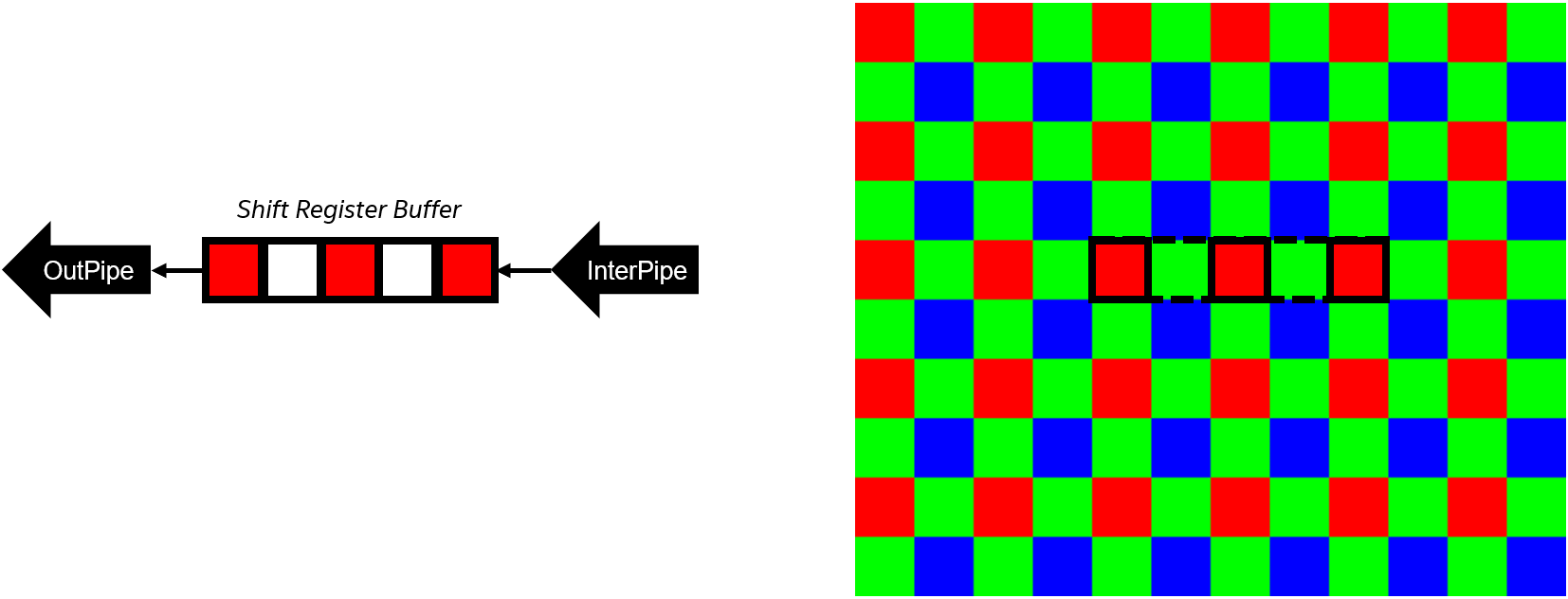

以下に示す Horizontal Kernel のロジックは、一度に 1 行ずつ操作するため、より単純です。

入力データを生成して出力を使用するため、設計では次の図に示すように完全なシステムをセットアップします。Input Kernel はデバイスメモリーから入力データを読み取り、入力パイプを介して ANR デザインに提供します。Output Kernel は出力パイプから ANR デザインの出力を読み取り、デバイスメモリーに書き込みます。次に、oneAPI ホストコードは出力データを使用して、ピーク信号対雑音比 (PSNR) を使用したゴールデンリザルトに対して ANR アルゴリズムの精度を検証します。(詳細については、Wikipedia のピーク信号対雑音比 (PSNR) に関する記事を参照してください。)

量子化浮動小数点(QFP)

浮動小数点値は、符号ビット、指数、仮数で構成されます。この設計では、32 ビットの単精度浮動小数点値を取得し、より少ないビット数の量子化浮動小数点 (QFP) 値に変換します (詳細については、Wikipedia の単精度浮動小数点数の記事を参照してください)。

この設計のすべての QFP は合計 10 ビットですが、指数と仮数には異なる数値を使用します。この変換の目的は、指数関数 (exp(x)) や反転 (1/x) など高価な 32 ビット浮動小数点演算を近似するためルックアップ・テーブル (LUT) 読み取り専用メモリー (ROM) を作成できるようにすることです。32 ビット浮動小数点用の LUT ROM を作成するには、オンチップメモリー 2^32*4 = 17GB バイトが必要になります。浮動小数点数を 10 ビットに量子化できる場合、精度は低下しますが、オンチップメモリー 2^10*4 = 4KB のみが必要となります。

ソースコードの内訳

以下のソースファイルは、src ディレクトリーにあります。

| ファイル | 説明 |

|---|---|

main.cpp |

main() 関数と、トップレベルの起動、検証、およびパフォーマンス測定が含まれます。 |

anr_params.hpp |

シグマ係数、フィルターサイズ、アルファー値などの ANR 固有のパラメーターを解析して保持するクラス。 |

anr.hpp |

すべての ANR カーネルをキューに送信するロジックと、バイラテラル・フィルター (水平と垂直の両方) のトップレベルの説明が含まれます。 |

column_stencil.hpp |

列ステンシル (1D 垂直畳み込み) を計算する汎用ライブラリー。 |

constants.hpp |

ANR アルゴリズムの定数とデータ型が含まれます。 |

data_bundle.hpp |

カーネル間で移動するデータをバンドルする汎用ライブラリーであり、基本的には配列です。 |

dma_kernels.hpp |

ホストとデバイス間でデータを移動したり、FPGA とデバイスメモリー間でデータを読み書きするカーネルが含まれています。 |

intensity_sigma_lut.hpp |

強度シグマ値用の RAM LUT。 |

qfp_exp_lut.hpp |

32 ビット浮動小数点値 (QFP を使用) で exp(-x) を計算する ROM LUT。 |

qfp_inv_lut.hpp |

32 ビット浮動小数点値 (QFP を使用) で 1/x を計算する ROM LUT。 |

qfp.hpp |

32 ビット浮動小数点と量子化浮動小数点 (QFP) 間の変換を行う汎用静的メソッドを持つクラスが含まれています。 |

row_stencil.hpp |

行ステンシル (1D 水平畳み込み) を計算する汎用ライブラリー。 |

shift_reg.hpp |

シフトレジスター用の汎用ライブラリー。 |

constexpr_math.hpp、unrolled_loop.hpp、および rom_base.hpp については、DirectProgramming/C++SYCL_FPGA/include/ ディレクトリー内の README を参照してください。

再利用可能なヘッダーファイル

この設計では、次の汎用ヘッダーファイルを使用します。

注: これらのヘッダーファイルの一部は

/DirectProgramming/C++SYCL_FPGA/includeフォルダーにあります。プログラムを正しくコンパイルするには、それらの一部をリファレンス・デザインのsrcサンプル・ディレクトリーにコピーする必要がある場合があります。

| ファイル | 説明 |

|---|---|

ColumnStencil (column_stencil.hpp) |

フィルターを実行するためコールバック用の C++ 関数を使用して、列ステンシル (つまり、垂直フィルター) を一般化するライブラリー。このライブラリーは、FIFO ラインストアとパディングロジックの詳細を隠匿し、ユーザーがフィルターの畳み込みだけに集中できるようにします。 |

DataBundle (data_bundle.hpp) |

同じデータを複数保持するライブラリー。このクラスは C++ std::array に似ていますが、コストのかかるループを回避するためコンストラクターと operator= が適切にオーバーライドされることを保証します。 |

ROMBase (rom_base.hpp) |

このライブラリーは、FPGA 内の ROM となる constexpr クラスを作成する基本クラスを提供します。 |

UnrolledLoop (unrolled_loop.hpp) |

C++ メタ・プログラミングを使用してフロントエンドのアンロールループを実装するライブラリー。 |

mp_math.hpp |

C++ メタ・プログラミングを使用して実装されたさまざまな constexpr 数学関数のセット。 |

注: これらのヘッダー・ライブラリーの使用方法と実装の詳細については、

.hppファイル内のソースコードのコメントを参照してください。

Adaptive Noise Reduction リファレンス・デザインをビルド

注: コマンドライン・インターフェイス (CLI) を使用する場合、環境変数を使用して oneAPI ツールキットを構成する必要があります。新しいターミナルウィンドウを開くたびに

setvarsスクリプトを実行して、CLI 環境を設定します。この方法により、コンパイラー、ライブラリー、およびツールの開発準備が整っていることが保証されます。Linux:

- システム全体へのインストールの場合:

. /opt/intel/oneapi/setvars.sh- プライベート・インストールの場合:

. ~/intel/oneapi/setvars.sh- csh などの非 POSIX シェルでは、次のコマンドを使用します:

bash -c 'source <install-dir>/setvars.sh ; exec csh'Windows:

C:\"Program Files (x86)"\Intel\oneAPI\setvars.bat- Windows PowerShell で次のコマンドを使用します:

cmd.exe "/K" '"C:\Program Files (x86)\Intel\oneAPI\setvars.bat" && powershell'環境変数の設定の詳細については、Linux* で setvars および oneapi-vars スクリプトを使用または Windows* で setvars および oneapi-vars スクリプトを使用を参照してください。

Linux

サンプル・ディレクトリーに移動します。

デフォルトである Agilex® 7 デバイスファミリー向けのビルドシステムを構成します。

mkdir build cd build cmake ..注: 次のコマンドでデフォルトのターゲットを変更できます:

cmake .. -DFPGA_DEVICE=<FPGA device family or FPGA part number>あるいは、次のコマンドで明示的な FPGA ボードバリアントと BSP をターゲットにすることもできます:

cmake .. -DFPGA_DEVICE=<board-support-package>:<board-variant> -DIS_BSP=1

注:

aoc -list-boardsコマンドを使用して、システムで利用可能な BSP をポーリングできます。プリントされるボードリストは次の形式になります。$> aoc -list-boards Board list: <board-variant> Board Package: <path/to/board/package>/board-support-package <board-variant2> Board Package: <path/to/board/package>/board-support-packageBSP を指定した場合のみ、FPGA 上で実行可能ファイルを実行できます。

デザインをコンパイルします。(提供されたターゲットは、推奨される開発フローと一致しています。)

エミュレーション用にコンパイルします (コンパイル時間が短く、エミュレートされた FPGA デバイスをターゲットにします):

make fpga_emuシミュレーション用にコンパイルします (コンパイル時間が短く、シミュレーター FPGA デバイスをターゲットにします):

make fpga_simHTML パフォーマンス・レポートを生成します。

make reportレポートは

anr.report.prj/reports/report.htmlにあります。FPGA ハードウェア用にコンパイルします (コンパイル時間が長く、FPGA デバイスをターゲットにします)。

make fpga

Windows

サンプル・ディレクトリーに移動します。

デフォルトである Agilex® 7 デバイスファミリー向けのビルドシステムを構成します。

mkdir build cd build cmake -G "NMake Makefiles" ..注: 次のコマンドでデフォルトのターゲットを変更できます:

cmake -G "NMake Makefiles" .. -DFPGA_DEVICE=<FPGA device family or FPGA part number>あるいは、次のコマンドで明示的な FPGA ボードバリアントと BSP をターゲットにすることもできます:

cmake -G "NMake Makefiles" .. -DFPGA_DEVICE=<board-support-package>:<board-variant> -DIS_BSP=1

注:

aoc -list-boardsコマンドを使用して、システムで利用可能な BSP をポーリングできます。プリントされるボードリストは次の形式になります。$> aoc -list-boards Board list: <board-variant> Board Package: <path/to/board/package>/board-support-package <board-variant2> Board Package: <path/to/board/package>/board-support-packageBSP を指定した場合のみ、FPGA 上で実行可能ファイルを実行できます。

デザインをコンパイルします。(提供されたターゲットは、推奨される開発フローと一致しています。)

エミュレーション用にコンパイルします (コンパイル時間が短く、エミュレートされた FPGA デバイスをターゲットにします):

nmake fpga_emuシミュレーション用にコンパイルします (コンパイル時間が短く、シミュレーター FPGA デバイスをターゲットにします):

nmake fpga_simHTML パフォーマンス・レポートを生成します。

nmake reportレポートは

anr.report.prj/reports/report.htmlにあります。FPGA ハードウェア用にコンパイルします (コンパイル時間が長く、FPGA デバイスをターゲットにします)。

nmake fpga

注: Windows でコンパイルする際に長いパスによる問題が発生する場合、たとえば

C:\samples\buildのように、より短いパスで ‘build’ ディレクトリーを作成します。次に、そのディレクトリーで cmake を実行し、サンプル・ディレクトリーへのフルパスを cmake に指定します。次に例を示します:C:\samples\build> cmake -G "NMake Makefiles" C:\long\path\to\code\sample\CMakeLists.txt

Adaptive Noise Reduction ファイルを実行します

Linux

FPGA エミュレーターでサンプルを実行します (カーネルは CPU 上で実行されます)。

./anr.fpga_emuFPGA シミュレーター・デバイスでサンプルを実行します。

CL_CONTEXT_MPSIM_DEVICE_INTELFPGA=1 ./anr.fpga_simまたは、FPGA デバイスでサンプルを実行します (

cmakeを-DFPGA_DEVICE=<board-support-package>:<board-variant>で実行した場合のみ)。./anr.fpga

Windows

FPGA エミュレーターでサンプルを実行します (カーネルは CPU 上で実行されます)。

anr.fpga_emu.exeFPGA シミュレーター・デバイスでサンプルを実行します。

set CL_CONTEXT_MPSIM_DEVICE_INTELFPGA=1 anr.fpga_sim.exe set CL_CONTEXT_MPSIM_DEVICE_INTELFPGA=または、FPGA デバイスでサンプルを実行します (

cmakeを-DFPGA_DEVICE=<board-support-package>:<board-variant>で実行した場合のみ)。anr.fpga.exe

出力例

Runs: 2

Columns: 1920

Rows: 1436

Frames: 8

Filter Size: 9

Pixels Per Cycle: 2

Maximum Columns: 2048

Execution time: 45.0012 ms

Throughput: 488.876 MB/s

PASSED注: FPGA エミュレーターで実行する場合、実行時間とスループットは設計のハードウェア・パフォーマンスを反映しません。

ライセンス

サンプルコードは、MIT ライセンスに基づいてライセンスされます。詳細は、License.txt (英語) を参照してください。

サードパーティー・プログラムのライセンスは、third-party-programs.txt (英語) で確認できます。