右上にあるこのウィンドウを使用して並列サイトを調査します。サイトを選択して、アノテーションと関連する特性を表示します。サイトのリストを「行うべきリスト」として使用します。上から順に進めます。

コントロール

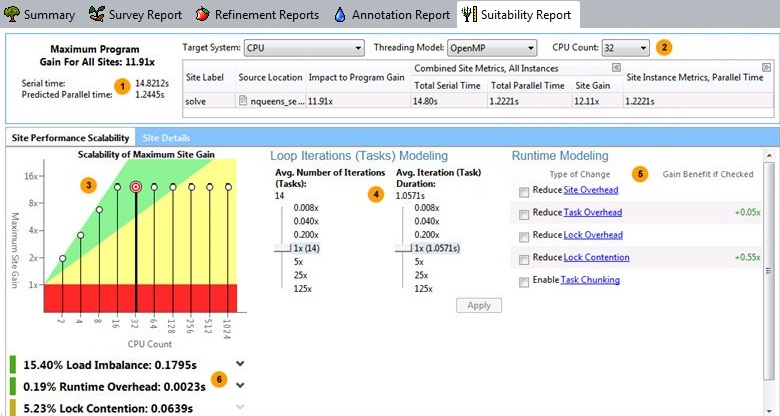

このスクリーンショットには、[Target System (ターゲットシステム)] が [CPU] の場合のデータが表示されています。実際のシステムでの実行結果は異なります。

|

左上のエリアはプログラムの [Maximum Program Gain for All Sites (すべてのサイトの最大プログラムゲイン)] を表示します。並列処理を実装する主な目的は、[Maximum Program Gain for All Sites (すべてのサイトの最大プログラムゲイン)] を増やし、並列プログラムの実行をより高速化することです。測定されたシリアル実行時間、予測並列実行時間、および測定されたポーズされた時間は、Maximum Program Gain for All Sites (すべてのサイトの最大プログラムゲイン) の下に表示されます。予測されたスータビリティー・ゲイン値を使用して、詳しい情報を得た上で並列処理を実装すべき場所を決定できます。 スータビリティー・ツールが検出したアノテーションに関連するエラーは、[Suitability Report (スータビリティー・レポート)] ウィンドウの上部に表示されます。エラーが発生した場合、表示されているスータビリティー・データの信頼性は保証されません。アノテーションに関連するエラーは、アノテーションの不足により正しいシーケンスのアノテーションが実行されなかった場合、予期しない実行パスが実行された場合、またはスータビリティー・データ収集がターゲットの実行中にポーズされた場合に発生する可能性があります。 |

|

右上にある modeling parameters (モデル化パラメーター) を使用してパフォーマンスをモデル化します。ドロップダウン・リストから、ハードウェア構成とスレッド化モデル (並列フレームワーク) を選択します。[Target System (ターゲットシステム)] で、インテル® Xeon Phi™ プロセッサーを選択すると、追加の項目 [Coprocessor Threads (コプロセッサー・スレッド)] が表示されます。 この行の下のデータグリッドには、プログラム実行中に検出された各並列サイトのパフォーマンスの予測値が表示されます。[Site Label (サイトラベル)] には、サイト・アノテーションへの引数が示されます。[Maximum Program Gain for All Sites (すべてのサイトの最大プログラムゲイン)] への各サイトの貢献度を推測するため、[Site Gain (サイトゲイン)] と [Impact to Program Gain (プログラムゲインへの貢献度)] の予測 (高い値が良い) を調査します。[Combined Site Metrics (結合されたサイトメトリック)] または [Site Instance Metrics (サイト・インスタンス・メトリック)] の下にあるデータを展開するには、見出しの右にある 選択した並列サイトのソースコードを表示するには、[Suitability Source (スータビリティー・ソース)] ウィンドウを表示する行をクリックします。 コマンドツール・バーを表示/非表示にするには、 |

|

[Scalability of Maximum Site Gain (最大サイトゲインのスケーラビリティー)] グラフには、選択したサイトのパフォーマンス・サマリーが示されます。グラフの X 軸には、CPU プロセッサー数またはコプロセッサーのスレッド数の合計が示され、Y 軸にはターゲットの予測パフォーマンス・ゲインが示されます。デフォルトの [CPU Count (CPU 数)] と [Maximum CPU Count (最大 CPU 数)] を変更するには、オプション値を設定します。 [CPU] の [Target System (ターゲットシステム)] を選択した場合、タスクやロックと同様に選択したサイトの詳しい特性を見るには、[Site Details (サイト詳細)] タブをクリックします。 |

|

並列パフォーマンスを改善する異なるループ構造、反復数、およびインスタンスの存続時間を調査するには、[Loop Iterations (Tasks) Modeling (ループ反復 (タスク) のモデル化)] (または [Tasks Modeling (タスクのモデル化)]) の modeling parameters (モデル化パラメーター) を使用します。 例えば、入れ子のループ構造を変更したり、ループ本体のコードを変更したり、反復数を変更した場合の影響を確認したいこともあるでしょう。 タスク・アノテーションがタスク並列処理を示している場合、(データ並列処理を示す [ループ反復 (タスク) モデル化] の代わりに) [タスクのモデル化] が表示されます。 |

|

[Runtime Modeling (ランタイムのモデル化)] の モデル化パラメーター を使用して、どの並列オーバーヘッド・タイプが、並列パフォーマンスに影響するか調査します。後で選択した並列フレームワークの機能を使用するか、並列処理を実装した後に並列コードをチューニングして指摘されたカテゴリーに対処する場合、カテゴリーを確認します。 [Target System (ターゲットシステム)] で [Intel Xeon Phi (インテル® Xeon Phi™)] または [Offload to Intel Xeon Phi (インテル® Xeon Phi™ へオフロード)] を選択した場合、[Runtime Modeling (ランタイムのモデル化)] の下に [インテル® Xeon Phi™ 製品向けの高度なモデル化] オプションが表示されます。このオプションを展開するには、[インテル® Xeon Phi™ 製品向けの高度なモデル化] の右にある下方向の矢印をクリックします。 |

|

グラフの下には、予測されるパフォーマンス・ゲインを妨げる問題のリストとシリアルおよび予測並列時間が示されます。行を展開するには、項目名の右にある下矢印をクリックします。大部分の問題は、[Runtime Modeling (ランタイムのモデル化)] の モデル化パラメーター に関連します。後で、インテル® VTune™ プロファイラー などの解析ツールを使用して、並列プログラムの実際のパフォーマンスを測定できます。 |

アイコンをクリックします。データを折りたたむには見出しの右にある

アイコンをクリックします。データを折りたたむには見出しの右にある  をクリックします。

をクリックします。 または

または  アイコンをクリックします。

アイコンをクリックします。